随着电子技术的飞速发展,AXI总线协议已成为现代电子系统中不可或缺的一部分,特别是在嵌入式系统、处理器与外设之间的通信中,AXI协议以其高性能、低延迟的特点被广泛采用,AXI突发写(AXI Burst write)是AXI协议中的一种重要操作模式,而掌握其地址边界机制则是有效应用这一模式的关键。

AXI协议与突发写概述

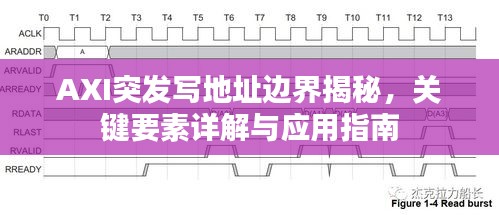

AXI(Advanced eXtensible Interface)是一种高性能、高吞吐量的通信协议,广泛应用于处理器与外设之间的数据传输,突发写(Burst write)是AXI协议中的一种数据传输模式,允许在连续的内存地址空间进行大量数据的快速传输,这种机制显著提高了数据传输效率,降低了系统延迟。

AXI突发写地址边界解析

在AXI突发写操作中,地址边界指的是在一次突发写操作中,数据传输的起始地址和结束地址之间的关系,理解并正确应用地址边界机制对于确保数据正确传输至关重要。

1、地址对齐:AXI突发写要求起始地址必须对齐,即地址必须是某个固定大小的整数倍,这有助于提高数据传输效率。

2、边界跨越:在某些情况下,AXI突发写可能会跨越内存页或缓存行边界,这时需要特别注意数据完整性,确保跨越边界的数据能够正确传输。

3、传输长度:突发写的传输长度应在AXI设备的支持范围内,超过设备支持的最大传输长度可能导致数据传输失败。

实际应用中的注意事项

在实际应用AXI突发写时,需要注意以下几个要点:

1、深入了解目标设备的AXI接口特性,包括支持的突发写大小、地址对齐要求等。

2、确保数据传输的起始地址和长度符合AXI设备的规范,避免地址越界或超出设备支持范围。

3、在进行跨越内存页或缓存行的突发写操作时,要特别注意数据完整性,确保数据的正确传输。

4、优化数据传输效率:通过合理设置突发写的大小和频率,可以优化数据传输效率,降低系统延迟。

AXI突发写地址边界机制是有效应用AXI协议的关键之一,在实际应用中,需要深入了解目标设备的AXI接口特性,确保数据传输的起始地址、长度和边界符合规范,要注意优化数据传输效率,降低系统延迟,通过正确理解和应用AXI突发写地址边界机制,可以充分发挥AXI协议的优势,提高电子系统的性能。

展望

随着电子技术的不断发展,AXI协议的应用将越来越广泛,对于AXI突发写地址边界机制的研究和应用将更加注重性能和效率的优化,随着新型存储技术的发展,AXI协议与新兴存储技术的结合将带来更多挑战和机遇,深入研究和理解AXI突发写地址边界机制对于未来的电子系统设计具有重要意义。

转载请注明来自武汉贝贝鲜花礼品网,本文标题:《AXI突发写地址边界揭秘,关键要素详解与应用指南》

蜀ICP备2022005971号-1

蜀ICP备2022005971号-1

还没有评论,来说两句吧...